Turbo-codes série

4.2. Turbo-codes série#

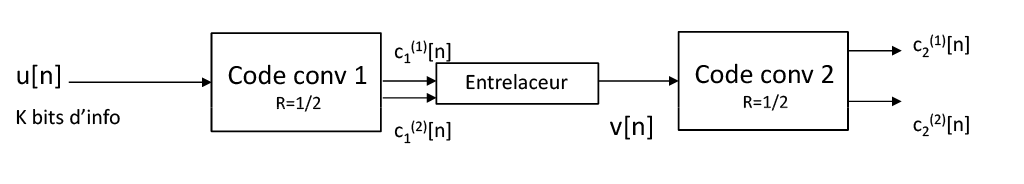

Fig. 4.3 Structure d’un turbo-code série avec deux codeurs.#

La figure Fig. 4.3 représente une autre concaténation possible à savoir la concaténtaion série. Le processus à l’émetteur est le suivant

\(K\) bits d’information sont codés avec le codeur \(1\) (code externe),

les bits codés sont entrelacés et puis codés par le codeur \(2\) (code interne).

Dans ce cadre, on a un rendement global (hors poinçonnage) correspondant au produit des rendements des deux codes internes

où \(R_i\) (resp. \(R_o)\) est le rendement du code interne (resp. externe).

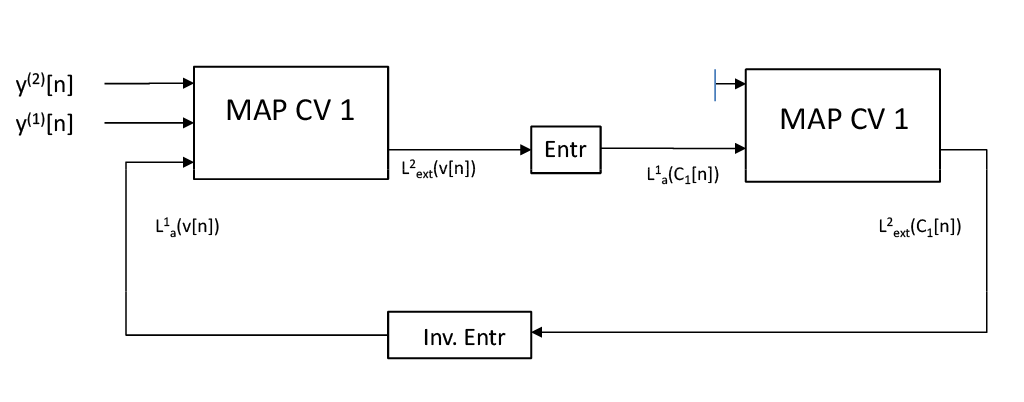

L’architecture du décodeur est alors donnée par la figure Fig. 4.4:

Fig. 4.4 Structure du décodeur itératif pour la concaténation série#

Les principales différences par rapport au cas de la concaténation parallèle sont les suivantes:

les deux décodeurs associés différents du cas parallèle,

le premier codeur peut le pas ètre récursif.

Pour le décodage, le décodeur souple associé au code interne est le même que celui d’un turbo-code parallèle, ie. que l’on donne une information souple sur les bits d‘“information” du codeur interne. Pour le code interne, le décodeur doit fournir une information extrinsèque sur l’ensemble des bits codés et non plus seulement sur les bits d’information. Le critère MAP associé est alors modifié de la manière suivante

où l’on a les notations suivantes: